# I<sup>2</sup>C real-time clock/calendar chip

#### **Features**

- Can time seconds, minutes, hours, weekdays, days, months, and years based on a 32.768kHz crystal

- Includes a century flag

- Wide operating voltage range: 1.8 to 5.5V

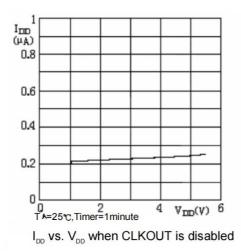

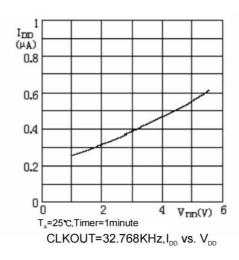

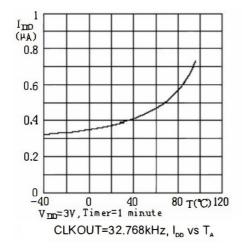

- Low standby current: typical value of 0.25μA (V<sub>DD</sub>=3.0V, T<sub>A</sub>=25°C)

- I<sup>2</sup>C bus address: Read, 0A3H; Write, 0A2H

- Programmable clock output frequencies: 32.768kHz, 1024Hz, 32Hz, 1Hz

- Alarm and timer functions

- Power-fail detector

- Internal integrated oscillator capacitor

- Open-drain interrupt pin

- Fully compatible with SL8563x

## **Applications**

- Portable media player

- Mobile phone

- Prepaid electric meter, IC card water meter, IC card gas meter

- Fax machine

- Security electronics

### **Description**

The SL8563x is a low-power CMOS real-time clock/calendar chip that features a programmable clock output, an interrupt output, and a power-fail detector. All addresses and data are serially transmitted via an I<sup>2</sup>C bus interface. The maximum bus speed is 400Kbits/s, and the embedded byte-addressable register automatically increments after each read or write operation.

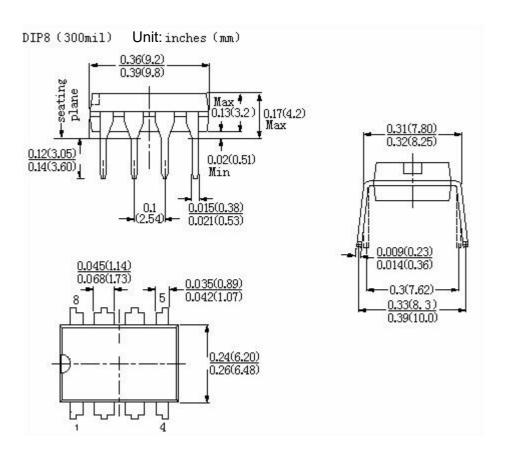

### Typical application circuit diagram

Fig.1 Typical Application Circuit Diagram

www.slkoric.com

1

# **Block diagram and pin functions**

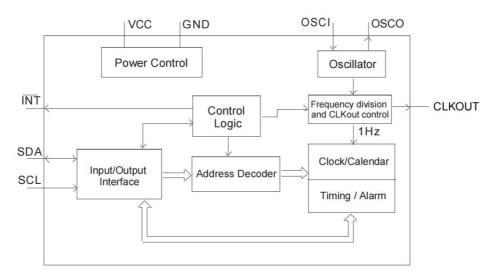

Fig.2 Block Diagram

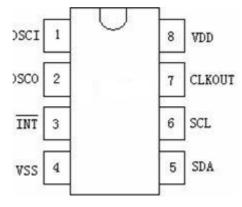

Fig.3 Pinout

## **Pin Description**

| Pin Number | Symbol          | Description                   | Pin Number | Symbol   | Description               |

|------------|-----------------|-------------------------------|------------|----------|---------------------------|

| 1          | OSCI            | oscillator input              | 5          | SDA      | serial data I/O           |

| 2          | o <u>sc</u> o   | oscillator output             | 6          | SCL      | serial clock input        |

| 3          | INT             | interrupt output (open drain) | 7          | CLKOUT   | clock output (open drain) |

| 4          | $V_{\text{SS}}$ | ground                        | 8          | $V_{DD}$ | positive power supply     |

${\it www.slkoric.com} \\ {\it 2}$

# **Maximum Ratings**

| Parameter                              | Symbol          | Min. | Max.                 | Unit       |

|----------------------------------------|-----------------|------|----------------------|------------|

| Power supply voltage                   | $V_{DD}$        | -0.5 | +6.5                 | W          |

| Power supply current                   | I <sub>DD</sub> | -50  | +50                  | mA         |

| Input voltage for SCL and SDA pins     | Vı              | -0.5 | +6.5                 | V          |

| Input voltage for OSCI pin             | VI              | -0.5 | V <sub>DD</sub> +0.5 | V          |

| Output voltage for CLKOUT and INT pins | Vo              | -0.5 | +6.5                 | V          |

| DC input current for all input ports   | l <sub>1</sub>  | -10  | +10                  | mA         |

| DC output current for all output ports | l <sub>o</sub>  | -10  | +10                  | mA         |

| Total power dissipation                | Р               |      | 300                  | mW         |

| Operating temperature                  | T <sub>A</sub>  | -40  | +85                  | $^{\circ}$ |

| Storage temperature                    | Ts              | -65  | +150                 | $^{\circ}$ |

## **Electrical characteristics parameters**

## **DC** electrical characteristics

(unless otherwise specified, Vn=1.8~5.5V, Vs=0V, Ta=-40~+85°C, fe=32.768kHz, quartz crystal Rs=40kΩ, CL=BpF).

| Parameter                                                 | Symbol           | Conditions                                                               | Min.               | Тур. | Max.               | Unit |  |  |

|-----------------------------------------------------------|------------------|--------------------------------------------------------------------------|--------------------|------|--------------------|------|--|--|

| Power Supply                                              |                  |                                                                          |                    |      |                    |      |  |  |

| operating voltage                                         |                  | I <sup>2</sup> C bus<br>failure,T <sub>A</sub> =25°C <sup>[1]</sup>      | 1                  | -    | 5.5                | V    |  |  |

|                                                           | V <sub>DD</sub>  | l <sup>2</sup> C bus<br>valid,f=400kHZ <sup>[1]</sup>                    | 1.8                | -    | 5.5                | V    |  |  |

| operating voltage to provide reliable clock/calendar data |                  | T <sub>A</sub> =25℃                                                      | $V_{LOW}$          | -    | 5.5                | V    |  |  |

| working current 1                                         | I <sub>DD1</sub> | f <sub>SCL</sub> =400kHz                                                 | -                  | -    | 800                | -    |  |  |

| CLKOUT is valid (FE=1)                                    | וטטי             | f <sub>SCL</sub> =100kHz                                                 | -                  | -    | 200                | -    |  |  |

|                                                           |                  | f <sub>SCL</sub> ;=0Hz,T <sub>A</sub> =25°C                              |                    | -    | 1                  |      |  |  |

|                                                           |                  | V <sub>DD</sub> =5.0V                                                    | -                  | 275  | 550                | nA   |  |  |

|                                                           |                  | V <sub>DD</sub> =3.0W                                                    | -                  | 250  | 500                | nA   |  |  |

| working current 2 CLKOUT stop (FE=0)                      | I <sub>DD2</sub> | V <sub>DD</sub> =2.0V                                                    | -                  | 225  | 450                | nA   |  |  |

| (1 L=0)                                                   |                  | f <sub>SCL</sub> =0Hz,T <sub>A</sub> =-40~+85°C<br>V <sub>DD</sub> =5.0V |                    | 500  | 750                | nA   |  |  |

|                                                           |                  | V <sub>DD</sub> =3.0V                                                    | -                  | 400  | 650                | nA   |  |  |

|                                                           |                  | V <sub>DD</sub> =3.0V<br>V <sub>DD</sub> =2.0V                           | -                  | 400  | 600                | nA   |  |  |

|                                                           |                  | f <sub>SCL</sub> =0Hz,T <sub>A</sub> =25°C                               |                    | +00  | 1 000              | 11/1 |  |  |

|                                                           |                  | V <sub>DD</sub> =5.0V                                                    | -                  | 825  | 600                | nA   |  |  |

|                                                           |                  | V <sub>DD</sub> =3.0V                                                    | _                  | 550  | 1000               | nA   |  |  |

|                                                           |                  | V <sub>DD</sub> =2.0V                                                    | -                  | 425  | 800                | nA   |  |  |

| working current<br>3CLKOUT=32.768kHz                      | I <sub>DD3</sub> | f <sub>SCL</sub> =0Hz,T <sub>A</sub> =-40~+85°C                          |                    |      |                    |      |  |  |

|                                                           |                  | V <sub>DD</sub> =5.0V                                                    | -                  | 950  | 1700               | nA   |  |  |

|                                                           |                  | V <sub>DD</sub> =3.0V                                                    | -                  | 650  | 1100               | nA   |  |  |

|                                                           |                  | V <sub>DD</sub> =2.0V                                                    | -                  | 500  | 900                | nA   |  |  |

| Input                                                     |                  | T                                                                        |                    |      | 1                  |      |  |  |

| low level input voltage                                   | VIL              |                                                                          | Vss                | -    | 0.3V <sub>DD</sub> | V    |  |  |

| high level input voltage                                  | V <sub>IH</sub>  |                                                                          | 0.7V <sub>DD</sub> | -    | V <sub>DD</sub>    | V    |  |  |

| input leakage current                                     | ILI              | V=V <sub>DD</sub> or V <sub>SS</sub>                                     | -1                 | 0    | 1                  | μA   |  |  |

| input capacitance                                         | Cı               | [3]                                                                      | -                  | -    | 7                  | pF   |  |  |

| Output                                                    |                  | T                                                                        |                    |      | _                  |      |  |  |

| SDA low level output current                              | I <sub>OLS</sub> | V <sub>CE</sub> =0.4V,V <sub>DD</sub> =5.0V                              | -3                 | -    | -                  | mA   |  |  |

| INT low level output current                              | I <sub>OLI</sub> | V <sub>CE</sub> =0.4V,V <sub>DD</sub> =5.0V                              | -1                 | -    | -                  | mA   |  |  |

| CLKOUT low level output current                           | I <sub>OLC</sub> | V <sub>CE</sub> =0.4V,V <sub>DD</sub> =5.0V                              | -1                 | •    | -                  | mA   |  |  |

| CLKOUT high level output current                          | Іонс             | V <sub>CE</sub> =4.6V,V <sub>DD</sub> =5.0V                              | 1                  | -    | -                  | mA   |  |  |

| output leakage current                                    | I <sub>Lo</sub>  | V0=V <sub>DD</sub> or V <sub>SS</sub>                                    | -1                 | 0    | 1                  | μA   |  |  |

| Voltage detector                                          |                  |                                                                          |                    |      |                    |      |  |  |

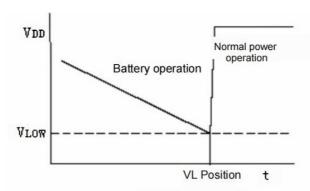

| power-off detection voltage                               | $V_{LOW}$        | Ta=25℃                                                                   | -                  | 0.9  | 1                  | V    |  |  |

<sup>1.</sup> Oscillator reliably starts upon power-up: VDD (minimum, power-up) = VDD (minimum) + 0.3V.

<sup>2.</sup> Timer source clock = 1/60Hz; both SCL and SDA are at VDD.

<sup>3.</sup> Tested based on samples.

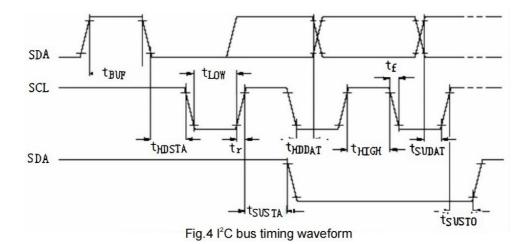

**AC** characteristics (unless otherwise specified,  $V_{DD}$  = 1.8~5.5V,  $V_{SS}$  = 0V;  $T_A$  = -40 to +85°C;  $f_{OSC}$  = 32.768KHz; quartz crystal Rs = 40k $\Omega$ ,  $C_L$  = 8pF).

| Parameter                           | Symbol                      | Conditions                                   | Min. | Тур.               | Max. | Unit |

|-------------------------------------|-----------------------------|----------------------------------------------|------|--------------------|------|------|

| Oscillator                          | ,                           |                                              |      |                    |      | -    |

| precision load capacitance          | CINT                        |                                              | 15   | 25                 | 35   | pF   |

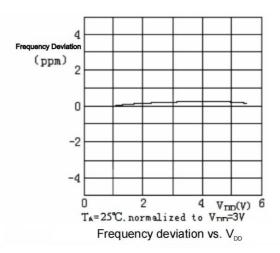

| oscillator stability                | $\triangle f_{osc}/f_{osc}$ | $\triangle V_{DD}$ =200mV,Ta=25 $^{\circ}$ C | _    | 2×10 <sup>-7</sup> |      | _    |

| Quartz crystal parameters(f=32.768) | (Hz)                        |                                              |      |                    |      |      |

| shenlian resistors                  | Rs                          |                                              | _    | _                  | 40   | kQ   |

| parallel loadcapacitance            | CL                          |                                              | _    | 10                 | _    | pF   |

| trimmer capacitor                   | Cı                          |                                              | 5    | _                  | 25   | pF   |

| CLKOUT Output                       |                             |                                              |      |                    |      |      |

| CLKOUT duty cycle                   | δ <sub>CLKOUT</sub>         | [1]                                          | _    | 50                 | _    | %    |

| I2C Bus Timing Characteristics      |                             |                                              |      |                    |      |      |

| SCL clock cycle                     | f <sub>scL</sub>            | [4]                                          | _    | _                  | 400  | kHz  |

| starting condition holding time     | thdsta                      |                                              | 0.6  | _                  | _    | μs   |

| repeated start condition setup time | tsusta                      |                                              | 0.6  | _                  | _    | μs   |

| SCL low level time                  | t <sub>Low</sub>            |                                              | 1.3  | _                  |      | μs   |

| SCL high time                       | t <sub>HIGH</sub>           |                                              | 0.6  | _                  |      | μs   |

| rising edge time of SCL and SDA     | t <sub>r</sub>              |                                              | _    | _                  | 0.3  | μs   |

| falling edge time of SCL and SDA    | t <sub>r</sub>              |                                              | _    | _                  | 0.3  | μs   |

| bus load capacitance                | Сь                          |                                              | _    | _                  | 400  | pF   |

| data setup time                     | t <sub>SUDAY</sub>          |                                              | 100  | _                  |      | ns   |

| data hold time                      | thdday                      |                                              | 0    | _                  |      | ns   |

| stop condition setup time           | t <sub>susтo</sub>          |                                              | 0.6  | _                  | _    | μs   |

| acceptable bus spike width          | t <sub>sw</sub>             |                                              | _    | _                  | 50   | ns   |

- 1. Unless otherwise specified,  $f_{CLKOUT} = 32.768kHz$ .

- 2. All timing values are valid within the operating voltage range ( $T_A$  condition). Refer to input voltage variations between  $V_{SS}$  and  $V_{DD}$  for  $V_{IL}$  and  $V_{IH}$  values.

- 3. Access time for I<sup>2</sup>C bus between two starts and one stop condition must be less than 1s.

# I<sup>2</sup>C bus timing waveform

## **Description**

The SL8563x features 16 8-bit registers, an auto-incrementing address register, a built-in 32.768kHz oscillator with an integrated capacitor, a prescaler for providing clock source to the real-time clock (RTC), a programmable clock output, a timer, an alarm, a brown-out detector, and a 400kHz I<sup>2</sup>C bus interface.

All 16 registers are designed as addressable 8-bit parallel registers, though not all bits are utilized. The first two registers (internal addresses 00H and 01H) serve as control and status registers. Addresses 02H to 08H are used for the clock counters (seconds through year counters), while addresses 09H to 0CH are allocated for alarm registers (defining alarm conditions). Address 0DH controls the output frequency of the CLKOUT pin, and addresses 0EH and 0FH are designated for the timer control and timer registers, respectively. The seconds, minutes, hours, day, month, year, minute alarm, hour alarm registers use BCD encoding format, while the weekday and weekday alarm registers do not use BCD encoding.

#### Alarm function mode

When one or more alarm register MSBs (AE = Alarm Enable) are cleared to 0, the corresponding alarm condition is valid, so that an alarm will be generated once every minute to once a week. Set the alarm flag bit AF (bit 3 of control/status register 2) to generate an interrupt. AF can only be cleared by software.

#### **Timer**

The 8-bit countdown timer (address 0FH) is controlled by the timer control register (address 0EH, refer to Table 22). This register configures the timer's frequency (4096Hz, 64Hz, 1Hz, or 1/60Hz) and enables or disables the timer. The timer counts down an 8-bit binary number set by software. At the end of each countdown, the timer sets the TF flag (see Table 4), which triggers an interrupt (INT). Each countdown cycle generates a pulse as the interrupt signal. The TF timer flag can only be cleared through software. TI/TP (see Table 4) controls the conditions for interrupt generation. When reading the timer, it returns the current countdown value.

#### **CLKOUT Output**

The pin CLKOUT can output a programmable square wave. The CLKOUT frequency register (address 0DH, see Table 20) determines the frequency of the output square wave, which can be 32.768kHz (default), 1024Hz, 32Hz, or 1Hz. CLKOUT is an open-drain output pin that is active when powered and becomes high impedance when inactive.

#### Reset

SL8563x has a built-in reset circuit, which starts to work when the oscillator stops working. In the reset state, the I<sup>2</sup>C bus is initialized, and all registers (including address pointer) will be cleared except TF, VL, TD1, TD0, TESTC, and AE bits are set to logic 1.

## **Brownout detection and clock monitoring**

Figure 8. Power-Off Detection

The SL8563x integrates a brown-out detection circuit, where the VL bit (Voltage Low, bit 7 of the seconds register) is set to 1 when  $V_{DD}$  drops below  $V_{LOW}$ . This indicates potential inaccuracies in clock/calendar data. The VL flag can only be cleared via software. When  $V_{DD}$  slowly decreases (e.g., due to battery power) to  $V_{LOW}$ , VL is set, indicating a potential interrupt condition.

## Register structure

**Table 1. Register Overview**

| Address | Register Name             | Bit7                  | Bit6 | Bit5 | Bit4  | Bit3  | Bit2 | Bit1 | Bit0 |

|---------|---------------------------|-----------------------|------|------|-------|-------|------|------|------|

| 00H     | control/status register 1 | TEST                  | 0    | STOP | 0     | TESTC | 0    | 0    | 0    |

| 01H     | control/status register 2 | 0                     | 0    | 0    | TI/TP | AF    | TF   | AIE  | TIE  |

| 0DH     | CLKOUT frequency register | FE                    | _    | _    | _     | _     | _    | FD1  | FD0  |

| 0EH     | timer control register    | TE                    | _    | _    | _     | _     | _    | TD1  | TD0  |

| 0FH     | timer countdown register  | timer countdown value |      |      |       |       |      |      |      |

Bits marked with "—" are invalid, and bits marked with "0" should be set to logic 0.

**Table 2. BCD Format Register Overview**

| Address | Register Name | Bit7 | Bit6 | Bit5                        | Bit4                        | Bit3                        | Bit2         | Bit1 | Bit0 |

|---------|---------------|------|------|-----------------------------|-----------------------------|-----------------------------|--------------|------|------|

| 02H     | seconds       | VL   |      |                             | 00∼59BCD code format number |                             |              |      |      |

| 03H     | minutes       | _    |      |                             | 00∼59B                      | CD code fo                  | rmat numbe   | r    |      |

| 04H     | hours         | _    | _    |                             | 00~                         | 23BCD cod                   | le format nu | mber |      |

| 05H     | day           | _    | _    |                             | 01~                         | 31BCD cod                   | le format nu | mber |      |

| 06H     | weekday       | _    | _    | _                           | _                           | _                           |              | 0~6  |      |

| 07H     | monthcentury  | С    | _    | _                           |                             | 01∼12BCD code format number |              |      |      |

| 08H     | year          |      |      | (                           | 00∼99BCD                    | code format                 | t number     |      |      |

| 09H     | minute alarm  | AE   |      |                             | 00∼59BCD code format number |                             |              |      |      |

| 0AH     | hour alarm    | AE   | _    |                             | 00∼23BCD code format number |                             |              |      |      |

| 0BH     | day alarm     | AE   | _    | 01∼31BCD code format number |                             |                             |              |      |      |

| 0CH     | weekday alarm | AE   | _    | _                           | _                           | _                           |              | 0∼6  |      |

The position marked with "—" is invalid.

## Control/Status Register 1

Table 3.Control/Status Register 1 (Address 00H)Bit Description

| Position No. | Symbol | Description                                                                                                                                                  |

|--------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7            | TEST1  | TEST1=0:Normal mode TEST1=1:EXT_CLK Test Mode                                                                                                                |

| 5            | STOP   | STOP=0:RTCClock running;STOP=1:All RTC dividers are asynchronously set to logic 0, and the RTC clock stops running. (CLKOUT is still available at 32.768kHz) |

| 3            | TESTC  | TESTC=0:Power reset function disabled (set to logic O in normal mode) TESTC=1:Power reset function is effective                                              |

| 6,4,2~0      |        | The default value is logic 0.                                                                                                                                |

#### **Control/Status Register 2**

TF and AF bits:When an alarm occurs,AF is set to logic 1.Similarly,when the countdown of a timer reaches zero,TF is set to logic 1.Both bits can only be modified through software.If both timer and alarm interrupts are needed in an application,reading these two bytes can identify the interrupt source.To clear a bit within a write cycle and prevent flag rewriting,a logical AND operation should be performed.

TIE and AIE bits:These two bits are used to enable interrupt generation. When both AIE and TIE are set, interrupts are generated as a logical OR of these two bits.

Table 4.Bit Description of Control/Status Register 2(Address 01h)

| Position No. | Symbol | Description                                                                                                                                                                                                      |

|--------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7,6,5        |        | The default value is logic 0.                                                                                                                                                                                    |

| 4            | TI/TP  | TI/TP=0:When TF is valid,INT is valid (depending on the state of TIE) TI/TP=1:INT,pulse valid,see Table 5(depends on the state of TIE) Note:IfAF and AIE are both valid,INTis always valid                       |

| 3            | AF     | AF=0:During read operation,the alam flag is invalid;during write operation,the alarm flag is cleared;AF=1:During read operation,the alarm flag is valid;during write operation,the alarm flag remains unchanged. |

| 2            | TF     | TF=0:When reading,the timer flag is invalid;when writing,the timer flag is cleared;<br>TF=1:When reading,the timer flag is valid;when writing,the timer flag remains<br>unchanged                                |

| 1            | AIE    | AIE=0:Alarm interrupt is disabled AIE=1:alarm interrupt is enabled                                                                                                                                               |

| 0            | TIE    | TIE=0:Timer interrupt is disabled TIE=1:Timer interrupt is enabled                                                                                                                                               |

## Table 5.INT Operation(Bit TI/TP=1)

| Clock Source(Hz) | ~INTcyclel <sup>[1]</sup> |        |  |  |  |

|------------------|---------------------------|--------|--|--|--|

| Clock Source(Hz) | n=1²                      | n>1    |  |  |  |

| 4096             | 1/8192                    | 1/4096 |  |  |  |

| 64               | 1/128                     | 1/64   |  |  |  |

| 1                | 1/64                      | 1/64   |  |  |  |

| 1/60             | 1/64                      | 1/64   |  |  |  |

<sup>[1].</sup>TF and INT are both valid;[2].n is the value of the countdown timer.When n=0,the timer stops working.

## Seconds, minutes, and hours registers

Table 6. Seconds/VL Register (Address 02H) Bit Description

| Position No. | Symbol   | Description                                                                                                           |  |  |  |  |

|--------------|----------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 6~0          | (Second) | Represents the current second value in BCD format, ranging from 00 to 99. For example, 1011001 represents 59 seconds. |  |  |  |  |

| 7            | VL       | VL=0: Ensure accurate clock/calendar data,VL=1: Accurate clock/calendar data is not guaranteed                        |  |  |  |  |

Table 7. Minute Register (Address 03H) Bit Description

| Position No. | Symbol   | Description                                                              |

|--------------|----------|--------------------------------------------------------------------------|

| 7            | _        | invalid                                                                  |

| 6∼0          | (minute) | Represents the current minute value in BCD format, ranging from 00 to 59 |

Table 8. Hour Register (Address 04H) Bit Description

| Position No. | Symbol | Description                                                            |

|--------------|--------|------------------------------------------------------------------------|

| 7, 6         | _      | invalid                                                                |

| 5~0          | (Hour) | Represents the current hour value in BCD format, ranging from 00 to 23 |

## Day, weekday, month/century, and year registers

## Table 9. Day Register (Address 05H) Bit Description

| Position No. | Symbol | Description                                                                                                                                                                              |  |

|--------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7, 6         |        | invalid                                                                                                                                                                                  |  |

| 5~0          | (day)  | Represents the current day value in BCD format, ranging from 01 to 31. If the current year counter value is a leap year, 8563 automatically adds a value to February to make it 29 days. |  |

Table 10. Weekday Register (Address 06H) Bit Description

| Position No. | Symbol    | Description                                                                                  |  |

|--------------|-----------|----------------------------------------------------------------------------------------------|--|

| 7∼3          | _         | invalid                                                                                      |  |

| 2~0          | ()()(a)() | Represents the current week value, ranging from 0 to 6. See Table 11. These bits can also be |  |

| 2~0          | (Week)    | reallocated by the user.                                                                     |  |

**Table 11. Weekly Distribution Table**

| Day       | Bit 2 | Bit 1 | Bit 0 |

|-----------|-------|-------|-------|

| Sunday    | 0     | 0     | 0     |

| Monday    | 0     | 0     | 1     |

| Tuesday   | 0     | 1     | 0     |

| Wednesday | 0     | 1     | 1     |

| Thursday  | 1     | 0     | 0     |

| Friday    | 1     | 0     | 1     |

| Saturday  | 1     | 1     | 0     |

Table 12. Month/Century Register (Address 07H) Bit Description

|              | rable 12. Month/ochtary Register (Address 9711) Bit Bescription |                                                                                                                                                                                                                  |  |  |

|--------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Position No. | Symbol                                                          | Description                                                                                                                                                                                                      |  |  |

| 7            | С                                                               | Century bit: C=0 specifies the century as 20XX; C=1 specifies the century as 19XX, where "XX" is the value in the year register, see Table 14. When the year changes from 99 to 00, the century bit will change. |  |  |

| 6, 5         |                                                                 | invalid                                                                                                                                                                                                          |  |  |

| 4~0          | (Month)                                                         | Represents the current month value in BCD format, ranging from 01 to 12, see Table 13                                                                                                                            |  |  |

**Table 13. Monthly Allocation Table**

| The months | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------------|-------|-------|-------|-------|-------|

| January    | 0     | 0     | 0     | 0     | 1     |

| February   | 0     | 0     | 0     | 1     | 0     |

| March      | 0     | 0     | 0     | 1     | 1     |

| April      | 0     | 0     | 1     | 0     | 0     |

| May        | 0     | 0     | 1     | 0     | 1     |

| June       | 0     | 0     | 1     | 1     | 0     |

| July       | 0     | 0     | 1     | 1     | 1     |

| August     | 0     | 1     | 0     | 0     | 0     |

| September  | 0     | 1     | 0     | 0     | 1     |

| October    | 1     | 0     | 0     | 0     | 0     |

| November   | 1     | 0     | 0     | 0     | 1     |

| December   | 1     | 0     | 0     | 1     | 0     |

Table 14. Year Register (Address 08H) Bit Description

| Position No. | Symbol | Description                                                            |

|--------------|--------|------------------------------------------------------------------------|

| 7∼0          | (year) | Represents the current year value in BCD format, ranging from 00 to 99 |

## **Alarm Control Register**

When one or more alarm registers are written with valid minute, hour, day, or weekday values, and their corresponding AE (Alarm Enable) bits are logic 0, and these values match the current minute, hour, day, or weekday values, the AF (Alarm Flag) is set. AF retains this set state until cleared by software. Once cleared, AF can only be set again when the time increments and matches the alarm conditions once more. Alarm registers are ignored when their respective AE bits are set to logic 1.

Table 15. Minute Alarm Register (Address 09H) Bit Description

| Position No. | Symbol       | Description                                                                |  |

|--------------|--------------|----------------------------------------------------------------------------|--|

| 7            | AE           | AE=0, Minute alarm effective; AE=1, Minute alarm invalid                   |  |

| 6∼0          | Minute alarm | Represents the minute alarm value in BCD format, the value is $00{\sim}59$ |  |

Table 16. Hour Alarm Register (Address 0AH) Bit Description

| Position No. | Symbol     | Description                                                       |  |

|--------------|------------|-------------------------------------------------------------------|--|

| 7            | AE         | AE=0,Hour alarm effective;AE=1,Hour alarm invalid                 |  |

| 5~0          | Hour alarm | Represents the hour alarm value in BCD format, the value is 00~23 |  |

Table 17. Daily Alarm Register (Address 0BH) Bit Description

| Position I | No. Symbol  | Description                                                              |  |

|------------|-------------|--------------------------------------------------------------------------|--|

| 7          | AE          | AE=0,Daily alarm is effective;AE=1,Day alarm invalid                     |  |

| 5~0        | Daily alarm | Represents the daily alarm value in BCD format, with a value of 01 to 31 |  |

Table 18. Week Alarm Register (Address 0CH) Bit Description

| Position No. | Symbol       | Description                                                           |  |

|--------------|--------------|-----------------------------------------------------------------------|--|

| 7            | AE           | AE=0,Weekly alarm valid;AE=1,Week alarm invalid                       |  |

| 2~0          | Weekly alarm | Represents the weekday alarm value in BCD format, the value is 0 to 6 |  |

www.slkoric.com  $^{12}$

# **CLKOUT Frequency Register**

Table 19. CLKOUT Frequency Register (Address 0Dh) Bit Description

| Position No. | Symbol | Description                                                                                  |  |

|--------------|--------|----------------------------------------------------------------------------------------------|--|

| 7            | FE     | FE=0: CLKOUT outputs are disabled and set to high impedance FE=1: CLKOUT output valid        |  |

| 6~2          | _      | nvalid                                                                                       |  |

| 1            | FD1    | The frequency output pin (f <sub>CLKOUT</sub> ) used to control CLKOUT is shown in Table 20. |  |

| 0            | FD0    | The frequency output pin (f <sub>CLKOUT</sub> ) used to control CLKOUT is shown in Table 20. |  |

**Table 20. CLKOUT Frequency Selection Table**

| FD1 | FD0 | f <sub>CLKOUT</sub> |

|-----|-----|---------------------|

| 0   | 0   | 32.768kHz           |

| 0   | 1   | 1024Hz              |

| 1   | 0   | 32Hz                |

| 1   | 1   | 1Hz                 |

## **Countdown Timer Register**

The timer register is an 8-bit byte countdown timer, its validity determined by bit TE in the timer controller. The timer clock can also be selected via the timer controller. Other timer functions, such as interrupt generation, are controlled by Control/Status Register 2. To accurately read back the countdown value, the I<sup>2</sup>C bus clock SCL should be at least twice the frequency of the selected timer clock.

Table 21. Timer Control Register (Address 0EH) Bit Description

| Position No. | Symbol | Description                                                                                                                                                                                                         |  |

|--------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7            | TE     | TE=0: Timer invalid;                                                                                                                                                                                                |  |

|              |        | TE=1: Timer is valid.                                                                                                                                                                                               |  |

| 6∼2          | _      | useless                                                                                                                                                                                                             |  |

| 1            | TD1    | The timer clock frequency selection bits determine the clock frequency of the countdown timer, as specified in Table 22. When not in use, TD1 and TD0 should be set to "11" (1/60Hz) to minimize power consumption. |  |

| 0            |        |                                                                                                                                                                                                                     |  |

**Table 22. Timer Clock Frequency Selection**

| TD1 | TD0 | Timer Clock Frequency(Hz) |

|-----|-----|---------------------------|

| 0   | 0   | 4096                      |

| 0   | 1   | 64                        |

| 1   | 0   | 1                         |

| 1   | 1   | 1/60                      |

Table 23. Timer Countdown Value Register (Address 0FH) Bit Description

| Position No. | Symbol                | Description                                                |

|--------------|-----------------------|------------------------------------------------------------|

| 7∼0          | timer countdown value | Countdown value "n", countdown period = n/clock frequency. |

## **EXT\_CLK Test Mode**

The test mode is used for online testing, establishing test patterns, and controlling RTC operations. The test mode is initiated by setting bit TEST1 of Control/Status Register 1, where the CLKOUT pin becomes an input. In test mode, a frequency signal input through the CLKOUT pin replaces the internal 64Hz signal, with each 64 rising edges generating a 1-second time increment.

Note: When entering EXT\_CLK test mode, the clock is not synchronized with the internal 64Hz clock, and the prescaling state cannot be determined.

### **Operation examples**

- 1. Enter EXT\_CLK test mode by setting bit 7 of Control/Status Register 1 (TEST=1).

- 2. Set bit 5 of Control/Status Register 1 (STOP=1).

- 3. Clear bit 5 of Control/Status Register 1 (STOP=0).

- 4. Set the Time Register (seconds, minutes, hours, day, weekday, month/century, and year) to the desired values.

- 5. Provide 32 clock pulses to CLKOUT.

- 6. Read the Time Register and observe the first change.

- 7. Provide 64 clock pulses to CLKOUT.

- 8. Read the Time Register and observe the second change. If additional increments of the Time Register are required, repeat steps 7 and 8.

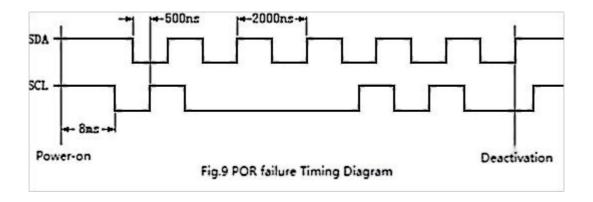

#### Power-On-Reset (POR) Failure Mode

The duration of POR (Power-On Reset) is directly related to the start-up time of the oscillator. An embedded circuit with an extended start-up time can disable POR, accelerating device testing. The signal waveforms for I<sup>2</sup>C bus pins SDA and SCL must adhere to the timings shown in Figure 9, where all timings represent minimum required values.

Upon entering the disabled mode, the chip immediately halts reset and transitions to EXT\_CLK test mode via the I<sup>2</sup>C bus. Clearing the TESTC bit (logic 0) eliminates the disabled mode, allowing re-entry into disabled mode only after setting TESTC to logic 1. Setting TESTC to logic 0 during normal operation is meaningless unless preventing entry into POR disabled mode is desired.

14

#### Serial interface

The SL8563x uses a serial I<sup>2</sup>C bus interface.

#### I<sup>2</sup>C Bus characteristics

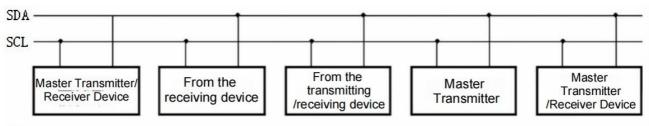

The  $I^2C$  bus communicates information between different chips and modules using two lines: SDA for serial data and SCL for serial clock. Both lines must be connected to a positive power source through a pull-up resistor. Data transmission occurs only when the bus is idle.

As depicted in Figure 10, the transmitting device generates information, the receiving device accepts it, the controlling device is the master, and the controlled device is the slave.

Fig. 10 I<sup>2</sup>C Bus System Configuration Diagram

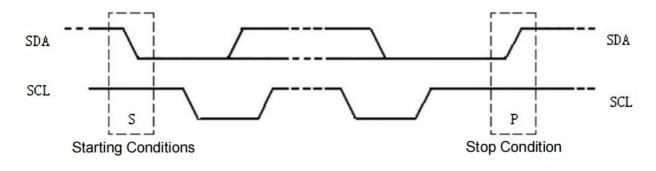

## Start (START) and stop (STOP) conditions

When the bus is idle, both the data line and the clock line maintain a high level. The start condition (S) occurs when the data line transitions from high to low during a high clock pulse. The stop condition (P) occurs when the data line transitions from low to high during a high clock pulse, as shown in Figure 11.

Fig.11 I<sup>2</sup>C Bus Start (Start) And Stop (Stop) Condition Definition

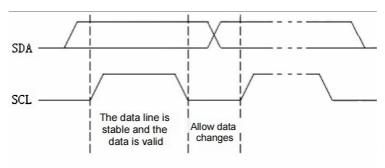

#### Bit transfer

Each clock pulse transmits one data bit, and the data on the SDA line should remain stable during the high phase of the clock pulse. Otherwise, the data on the SDA line could inadvertently become control signals, as referenced in Figure 12.

Fig. 12 Bit Transfer on the I2C Bus

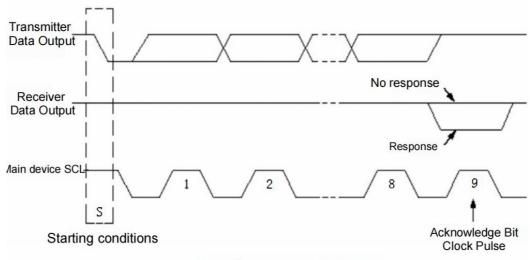

## Acknowledge bit

There is no limit to the number of data bytes a transmitter can send to a receiver between the start and stop conditions. After each 8-bit byte, an acknowledgment (ACK) bit is appended. The transmitter generates a high-level ACK bit, prompting the master device to produce an additional ACK clock pulse. The receiver must generate an ACK bit after receiving each byte, and the master receiver must also produce an ACK bit after receiving each byte transmitted by the transmitter. When the ACK clock pulse appears, the SDA line should remain at a low level (considering setup and hold times). The transmitter should transition to a low level when the last byte is received from the device, causing the receiver to generate an ACK bit, allowing the master device to generate a stop condition.

Fig.13 I2C Bus Acknowledge Bit

## I<sup>2</sup>C Bus protocol

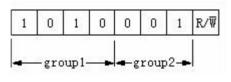

Note: Before transmitting data over the I<sup>2</sup>C bus, the receiving device must first acknowledge its address. Upon initiation of the I<sup>2</sup>C bus, this address is transmitted along with the first byte of data. The SL8563x can function as either a slave receiver or transmitter. In this mode, the clock signal line SCL functions strictly as an input signal line, while the data signal line SDA serves as a bidirectional signal line.

The slave address for the SL8563x is detailed in Figure 14.

Fig.14 Slave Address

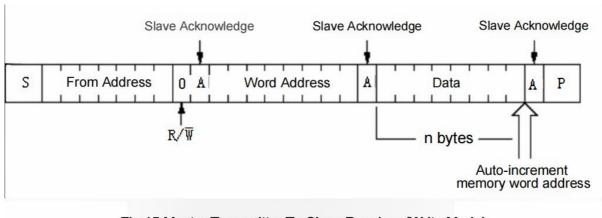

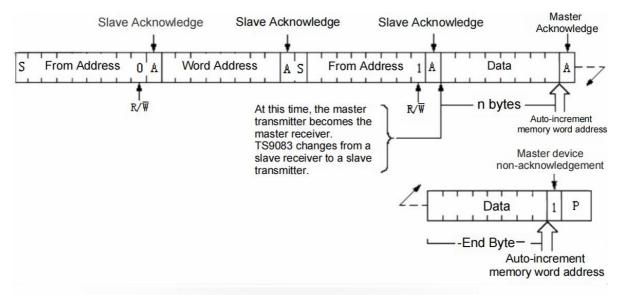

## Clock/calendar read/write cycles

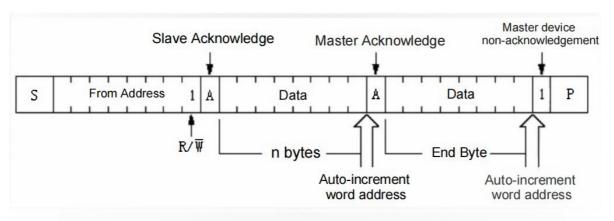

The serial I<sup>2</sup>C bus of SL8563x has three configuration options for read/write cycles, as depicted in Figures 15, 16, and 17. The address in these figures is a 4-bit number used to indicate the next register to access, with the upper four bits of the address being unused.

Fig.15 Master Transmitter To Slave Receiver (Write Mode)

Fig.16 Master Reads Data After Setting Word Address (Write Address, Read Data)

Fig.17 Master Reads Data After The First Byte Of Data From The Slave (Read Mode)

## Quartz crystal frequency adjustment

Method 1: Fixed OSCI Capacitor — Calculate the required average capacitance. Use this fixed capacitor value; upon powering, the frequency measured at the CLKOUT pin should be 32.768kHz. Deviation in the measured frequency depends on the quartz crystal, capacitor tolerance, and device variation (typically  $\pm 5 \times 10^{-6}$ ). Average deviation can be controlled within  $\pm 5$  minutes per year.

Method 2: OSCI Fine Tuning Capacitor — Achieve the precise oscillator frequency by adjusting the fine tuning capacitor on the OSCI pin. Upon powering, the frequency at the CLKOUT pin can be measured to be 32.768kHz.

Method 3: OSCO Output — Directly measure the output at OSCO (considering the capacitance of the test probe).

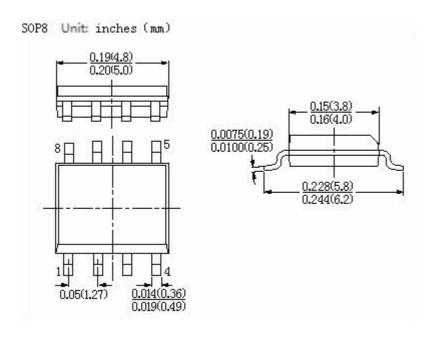

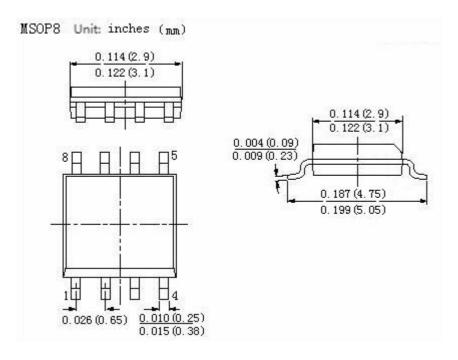

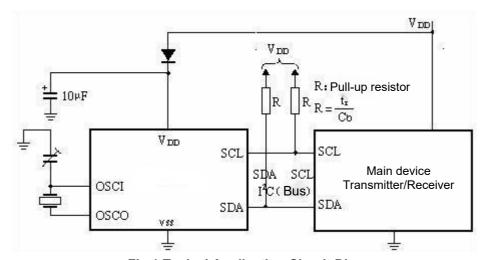

## **Ordering information**

| Model   | Temperature Range | Package |

|---------|-------------------|---------|

| SL8563D |                   | DIP8    |

| SL8563T | -40∼+85℃          | SOP8    |

| SL8563S |                   | MSOP8   |

## Package dimensions