Service hotline

+86 0755-83044319

release time:2023-10-13Author source:SlkorBrowse:11231

For the same task, the energy consumption of this chip for on-chip learning is only 3% of that of the Advanced Process-Specific Integrated Circuit (ASIC) system.

Currently, generative artificial intelligence has sparked a new wave of development in the AI industry. AI technologies supported by large computing power are greatly changing the way humans live and work. However, the massive number of parameters required for AI models has led to an increasing demand for computing power, making it imperative to find solutions to bridge the huge computing gap and achieve significant improvements in energy efficiency. High-performance and energy-efficient chips have become the specific carriers of computing power and the core foundation driving the development of this wave of intelligent revolution, as well as the driving force behind the continuous development of human society.

To address the major challenges faced by traditional storage-computing separation architectures that constrain computing power, Professor Wu Huaqiang and Associate Professor Gao Bin from the School of Integrated Circuits at Tsinghua University focused on the research of memory resistor storage-computing integrated technology and explored a new paradigm for computer systems.

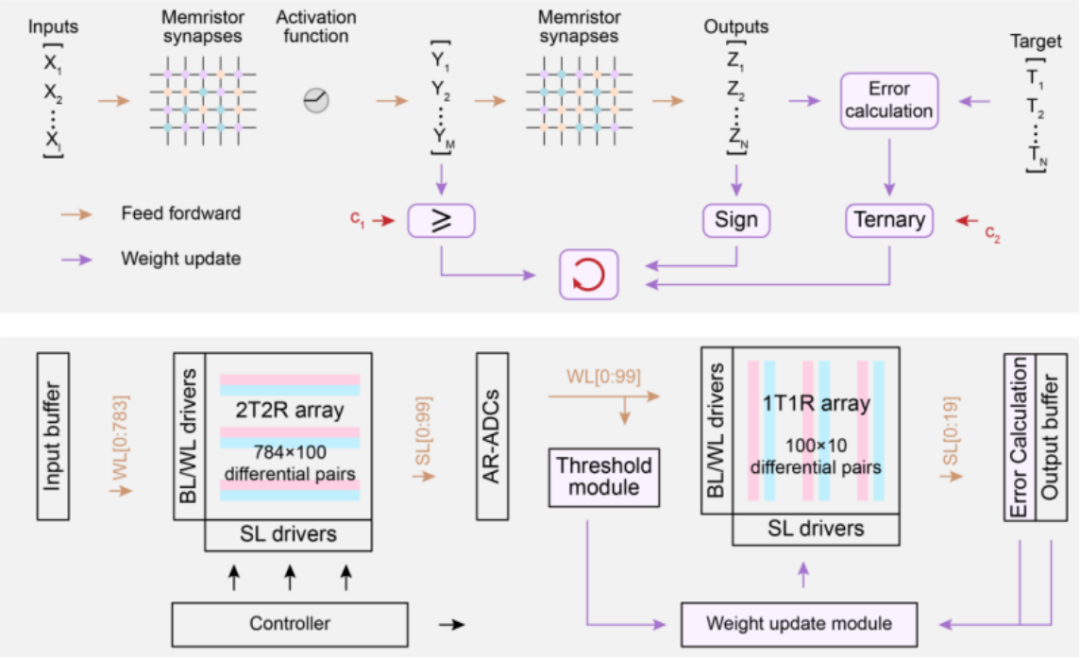

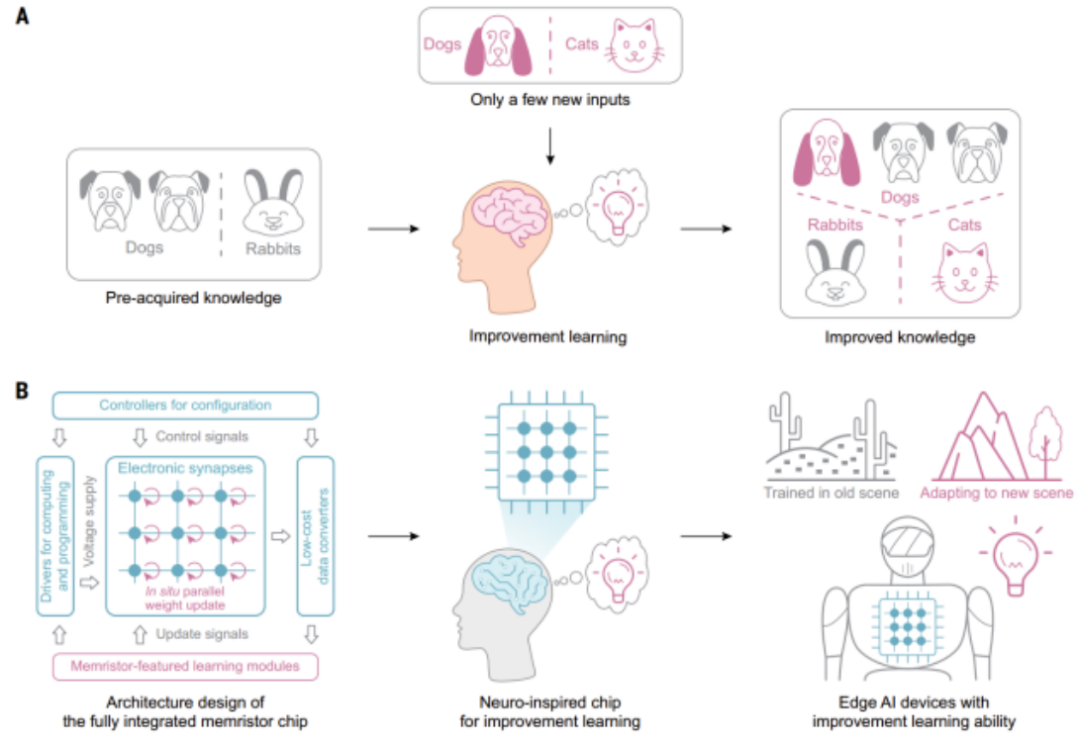

The memory resistor storage-computing integrated technology revolutionized the traditional von Neumann computing architecture from the aspects of device, circuit and theoretical computing, achieving a leap-forward improvement in computing power and energy efficiency. This technology can also utilize the learning characteristics of the underlying devices to support real-time on-chip learning, empowering new scenarios of local learning-based edge training. Currently, related research on the international level mainly focuses on learning function demonstrations at the memory resistor array level. However, the realization of globally integrated memory resistor chips supporting efficient on-chip learning still faces significant challenges, mainly due to the poor compatibility between the high-precision weight update method required by the traditional backpropagation training algorithm and the actual characteristics of memory resistors.

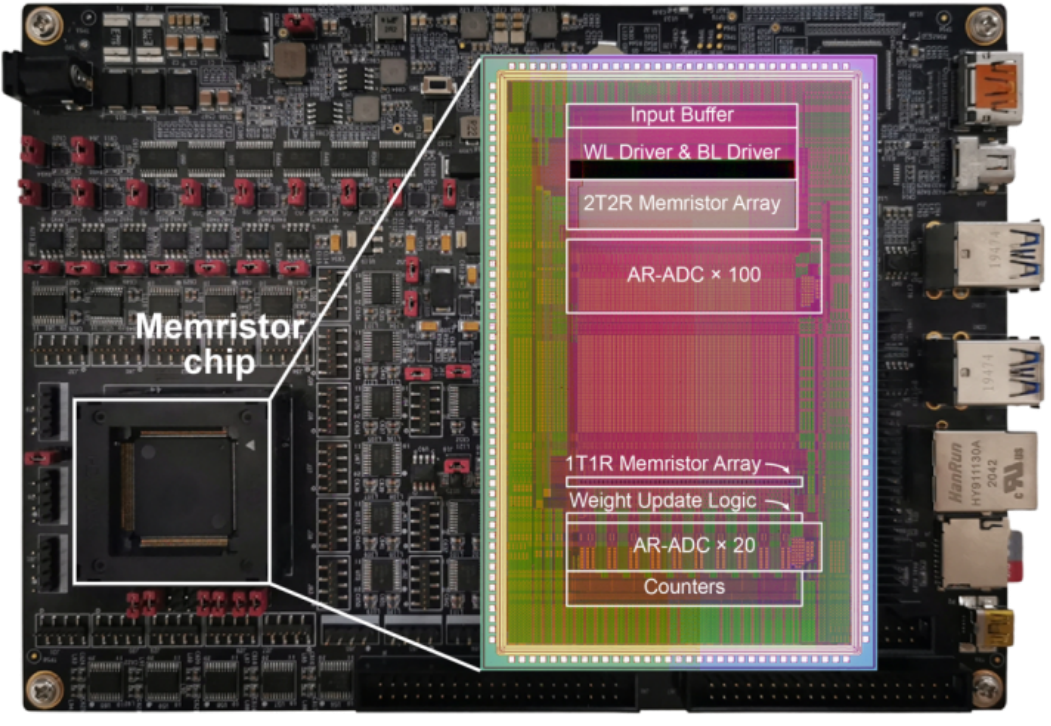

To solve the above problems, Professor Wu Huaqiang and Associate Professor Gao Bin based on the storage-computing integrated computing paradigm, developed the world's first globally integrated memory resistor storage-computing integrated chip that supports efficient on-chip learning (machine learning can be directly completed at the hardware end). They have made significant breakthroughs in the field of memory resistor storage-computing integrated chips supporting on-chip learning, which is expected to promote the development of artificial intelligence, autonomous driving and wearable devices. The relevant achievements have been published online in the latest issue of Science.

It is reported that this chip achieves an energy consumption for on-chip learning that is only 1/35 of that of the Advanced Process-Specific Integrated Circuit (ASIC) system, while also expected to achieve a 75-fold improvement in energy efficiency.

Universal algorithms and architectures based on memory-resistor storage-computing integration for efficient on-chip learning.

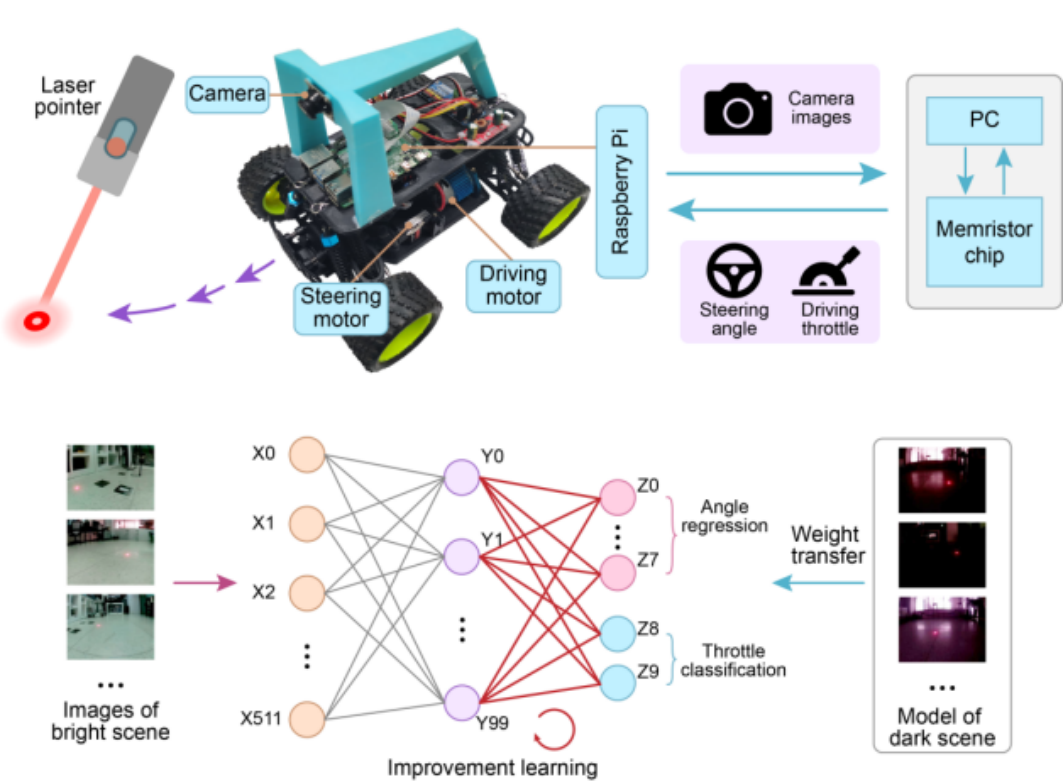

Demonstration of Incremental Learning for Automatic Tracking Control of a Small Car

For the same task, the energy consumption of on-chip learning achieved by this chip is only 3% of that of a specialized ASIC system under advanced technology, demonstrating outstanding energy efficiency advantages and great potential for meeting the high computing power demands of the AI era. This provides an innovative development path for breaking through the energy efficiency bottleneck under the traditional von Neumann computing architecture.

"The on-chip learning of storage and computation integration can effectively protect user privacy and data while achieving lower latency and smaller energy consumption," explained Dr. Yao Peng, a postdoctoral researcher. Referring to biomimetic brain processing methods, this chip can achieve fast "on-chip training" and "on-chip recognition" for different tasks, effectively performing incremental learning tasks in edge computing scenarios with low power consumption to adapt to new situations and learn new knowledge, meeting users' personalized needs.

For example, some people are accustomed to adding a short dash in the middle of the number "7". At first, the intelligent chip does not recognize this symbol, but after training on two or three such written "7"s, it can accurately recognize it as the number "7".

In the complex and ever-changing international situation, breaking through "bottleneck" technology remains a current focus.

Faced with practical problems such as a shortage of advanced research and development equipment, team members are somewhat at a loss as to whether each step they take is correct, whether the results can meet expectations, and whether the technology can be further optimized. All of these are huge burdens on everyone.

Firstly, there are technological challenges. The development of memristor chips involves cutting-edge knowledge from multiple disciplines such as materials science, physics, and electronic engineering. Among many technical challenges, the first one to be addressed is how to achieve large-scale integration of memristive devices. Through a large number of experiments and theoretical studies, the team proposed an architecture-circuit-process co-optimization method, which provided guidance for the design of storage and computation integrated system.

Secondly, there are engineering challenges. With the large-scale integration process and critical circuit design in place, how can errors caused by bottom-up multi-scale non-ideal effects be overcome and assembled into an efficient system chip? With the joint efforts of the team's teachers and students, the STELLAR architecture was proposed, algorithm optimization and simulation experiments were completed, and a highly efficient storage and computation integrated learning chip was fabricated, achieving a significant improvement in speed and energy efficiency.

.png)

"The road is difficult, but it holds extraordinary significance. It is an important battlefield in the current global high-tech field," Gao Bin believes. Chip research is a long and arduous process, with no apparent breakthrough in sight. However, through continuous research and learning, valuable achievements are obtained.

As the first authors of academic papers, Zhang Wenbin and Yao Peng have gained extensive knowledge in various research fields such as semiconductors, microelectronics, software algorithms, and neuromorphic computing during their doctoral studies. They have accumulated rich research and development results and valuable engineering experience.

From nothing to something, from weakness to strength. On this path of scientific research, which has no shortcuts, these "chip youth" have experienced countless moments of giving up after preparation and observation, only to start anew after numerous setbacks, overcoming one challenge after another.

Looking to the future, Wu Huaqiang hopes that the team's solutions and technologies can go beyond the laboratory and effectively promote the transformation of scientific research achievements. They are dedicated to serving the needs of the country and society.

Site Map | 萨科微 | 金航标 | Slkor | Kinghelm

RU | FR | DE | IT | ES | PT | JA | KO | AR | TR | TH | MS | VI | MG | FA | ZH-TW | HR | BG | SD| GD | SN | SM | PS | LB | KY | KU | HAW | CO | AM | UZ | TG | SU | ST | ML | KK | NY | ZU | YO | TE | TA | SO| PA| NE | MN | MI | LA | LO | KM | KN

| JW | IG | HMN | HA | EO | CEB | BS | BN | UR | HT | KA | EU | AZ | HY | YI |MK | IS | BE | CY | GA | SW | SV | AF | FA | TR | TH | MT | HU | GL | ET | NL | DA | CS | FI | EL | HI | NO | PL | RO | CA | TL | IW | LV | ID | LT | SR | SQ | SL | UK

Copyright ©2015-2025 Shenzhen Slkor Micro Semicon Co., Ltd